- Short Circuit Current Limit Adjustable

- Overload Breaking Current Adjustable

- I2C Communication

- Discrete Operation Option

#### **Electrical Specifications**

DC Input

Input: 0 to 50 V<sub>DC</sub>

Vcc: 3 to 5.5 Vpc

Vcc Supply Current: 25mA Typical

**Control**

• I2C Communication see • Open drain fault discrete signal • On/Off discrete signal

Note 1: Tested with full system

DC Output

• Input-to-Output impedance: Less than 2.5 m $\Omega$  @ 25  $^{\circ}C$

• Max load capacitance per channel:

Complies with MIL-STD-461F

(50μH LISN): RE102, CE102,

CS101<sup>1</sup>, CE101<sup>1</sup>, CS114<sup>1</sup>,

CS115<sup>1</sup>, CS116<sup>1</sup>, RS103<sup>1</sup>

<u>EMC</u>

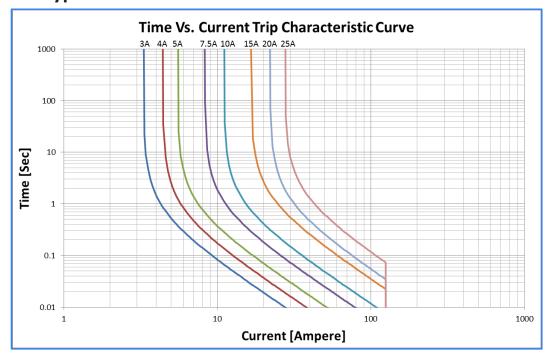

• Overload Breaking Current Adjustable from 2A to 30 A according to I2T curve.

• Short Circuit Current Limit Adjustable from 10 A to 125 A according to SCL curve.

#### Environmental 1

Design to Meet MIL-STD-810G

**Temperature**

Operating: –55°C to +125°C at ambient

Storage: -55°C to +125°C

Altitude

Method 500.5, Procedure I & II Storage/Air Transport: 40 kft Operation/Air carriage: 70 kft

Does not support fungus growth, in accordance with the guidelines of MIL-STD-454, Requirement 4.

Method 507.5, Up to 95% RH

Salt Fog:

Method 509.5

Shock1 Method 516.6

40g, 11msec saw-tooth (all

directions)

#### Vibration<sup>1</sup>

Figure 514.6E-1. General minimum integrity exposure. (1 hour per axis.)

Note 1: Tested with full system

#### Reliability

2,529,861 hours, calculated IAW MIL-HDBK-217F Notice 2 at +85°C, Ground fixed conditions.

# **Markets & Applications**

## **Functions and Signals**

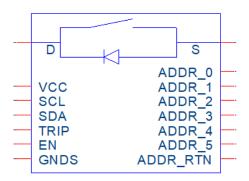

| Signal Name | M9526-100<br>Pinout | Description                                                                                     |  |  |

|-------------|---------------------|-------------------------------------------------------------------------------------------------|--|--|

| VCC         | 1                   | Control supply voltage with respect to GNDS.                                                    |  |  |

| SDA         | 2                   | I2C bus Data.                                                                                   |  |  |

| SCL         | 3                   | I2C bus Clock.                                                                                  |  |  |

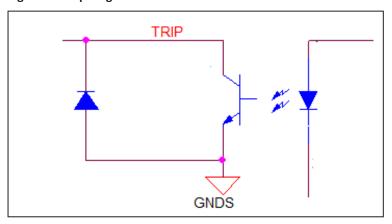

| TRIP        | 4                   | Open drain fault discrete signal. See Figure 1.                                                 |  |  |

| EN          | 5                   | The Enable signal is used to turn the SWITCH BRICK ON and OFF.                                  |  |  |

| ADDR_0      | 6                   | Used for Slave Device Addressing                                                                |  |  |

| ADDR_1      | 7                   | Used for Slave Device Addressing                                                                |  |  |

| ADDR_2      | 8                   | Used for Slave Device Addressing.                                                               |  |  |

| ADDR_3      | 9                   | Used for Slave Device Addressing.                                                               |  |  |

| ADDR_4      | 10                  | Used for Slave Device Addressing                                                                |  |  |

| ADDR_5      | 11                  | Used for Slave Device Addressing.                                                               |  |  |

| ADD_RTN     | 12                  | Used for Slave Device Addressing.                                                               |  |  |

| GNDS        | 14                  | ground for I2C, TRIP, EN and VCC.                                                               |  |  |

| D           | 15                  | Drain for Power Path. For positive voltage switch it will be the input voltage side connection. |  |  |

| S           | 16                  | Source for Power Path. For positive voltage switch it will be the load side connection.         |  |  |

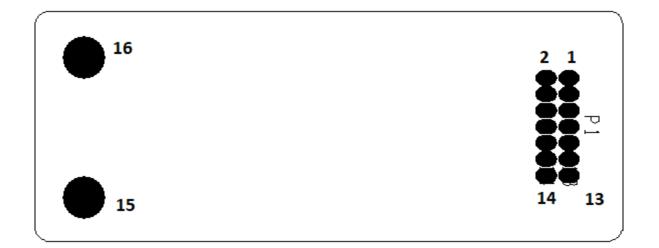

## Top View:

Figure 1 – Trip stage

## 1. Typical Tests Results

# 2. Typical Characteristics

Figure 2 - Time vs. Current Trip

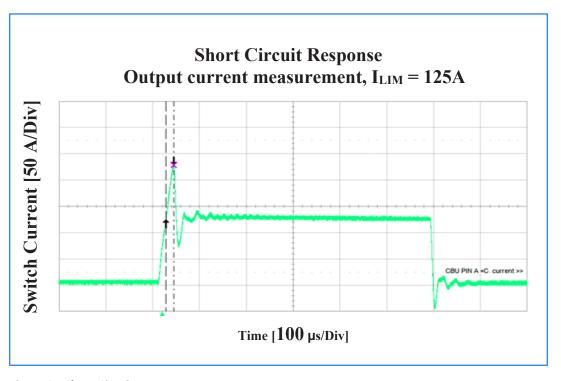

Figure 3 - Short Circuit Response

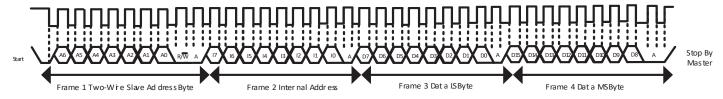

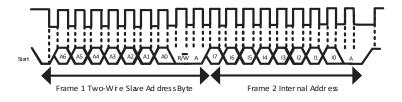

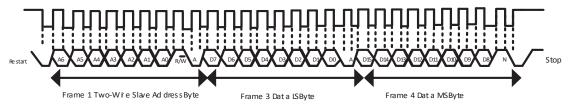

#### 1. I2C Protocol

Slave Address:

For  $0 \le ADDR \le 7 \rightarrow ADDR + 0x70$

For other Address = ADDR

Slave will be read as a memory device with one byte of internal address.

Byte order shall be little endian. For example, 01h address will be the LSB of VOUT1.

| Internal<br>Address | Name    | Function                    | R/W | Number of bytes | notes                                                                                                                                                                            |

|---------------------|---------|-----------------------------|-----|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00h                 | STAT    | Status Register             | R   | 1               | STAT[0] = Reset Flag (RST)  STAT[1] = Switch State ('1' = ON)  STAT[2] = Trip Status ('1' = Fault)  STAT[3] = Short Status ('1' = Trip from short circuit)  STAT[4:7] = Reserved |

| 01h                 | OUTCURR | Load Current<br>Measurement | R   | 2               | LSB = 62.5mA                                                                                                                                                                     |

| 03h                 | VOLTD   | Voltage Drop<br>Measurement | R   | 2               | LSB = 62.5mV                                                                                                                                                                     |

| 05h                 | TEMP    | Temperature<br>Measurement  | R   | 2               | LSB = 0.0625°C                                                                                                                                                                   |

| 07h                 | 12TACC  | I <sup>2</sup> t Status     | R   | 3               | I <sup>2</sup> t accumulator with respect to I2T_LIM                                                                                                                             |

| Oah | ĆTRL    | Control Register                    | RW | 1 | CTRL[0] = Switch Enable ('1' = En) CTRL[1] = Trip Reset ('1' = Reset) CTRL[2] = Reset Flag (RST, Reset value = '1') CTRL[4:7] = Battle Mode (0xD = Battle Enable)                             |

|-----|---------|-------------------------------------|----|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0bh | OLCL    | Overload Current<br>Limit           | RW | 2 | LSB = 62.5mA                                                                                                                                                                                  |

| Odh | I2T_LIM | Maximal I <sup>2</sup> t<br>Setting | WR | 3 | Thermal Constant(TC) is the trip time for twice of the overload current setting.  I2TACC can be set by following formula:  I2TACC = (IOVERLOAD*16) <sup>2</sup> *TC*16  TC [s], IOVERLOAD [A] |

| 10h | SCCL    | Short Circuit<br>Current Limit      | RW | 2 | LSB = 62.5mA                                                                                                                                                                                  |

## **Timing Diagram**

A[0:6] – Address D[0:15] – Data I[0:7] – Internal Address A – ACK N – NACK

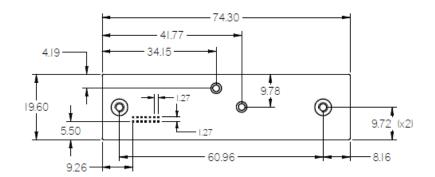

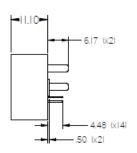

#### **Outline Drawing**

#### **Notes**

- Dimensions are in mm 1.

- Weight: 32g

- 3D model available

#### **Standard Configurations**

|             | Input                   | Output                   |                    |            |

|-------------|-------------------------|--------------------------|--------------------|------------|

| Part Number | Input Voltage range     | V <sub>cc</sub>          | Voltage            | Current    |

| PSD28V1CEC  | 0 to 50 V <sub>DC</sub> | 3 to 5.5 V <sub>DC</sub> | Following<br>Input | Adjustable |

Note: Specifications are subject to change without prior notice by the manufacturer.